AMD Ryzen 9000 – Part I – Arhitectura detaliata si modele

Arhitectura

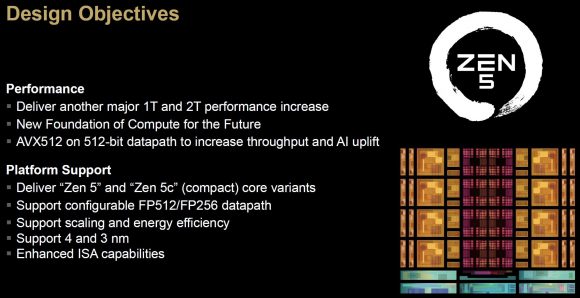

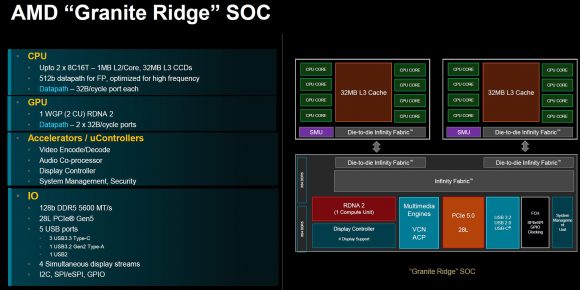

Arhitectura Zen 5 este derivata – asa cum era de asteptat – din Zen 4, insa vine cu imbunatatiri masive atat la front-end, cat si la motorul de executie sau back-end (incarcare / stocare).

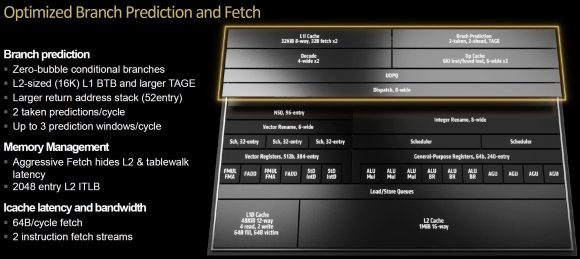

Unitatea de predictie a ramificatiilor (Branch Prediction) contribuie semnificativ la cresterea IPC-ului, prin urmare aceasta unitate primeste imbunatatiri in permanenta.

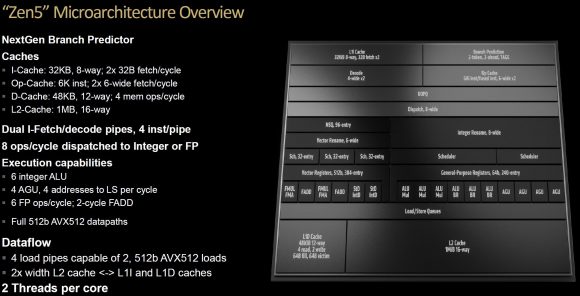

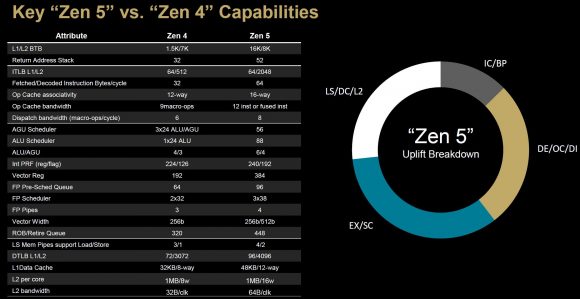

Desi cache-ul de instructiuni L1 si cache-ul operational (Op Cache) raman similare ca dimensiuni cu Zen 4, in ceea ce priveste latimea de banda si asociativitatea avem imbunatatiri.

Mai mult decat atat, acum avem doua OC (Op Cache) pipes pentru o capabilitate de 12 instructiuni / ciclu (2 x 6 instructiuni / ciclu), precum si doua cai de decodare. Acestea din urma sunt independente si paralele, prin urmare in modul SMT (cand avem 2 thread-uri ruland pe acelasi nucleu) fiecare thread primeste cate o cale distincta.

Modificarile aduse necesita mai multi tranzistori, insa procesul de fabricatie o permite, iar gratie acestora Zen 5 face mai multe predictii ale ramificatiilor per ciclu, iar calitatea acestora este imbunatatita.

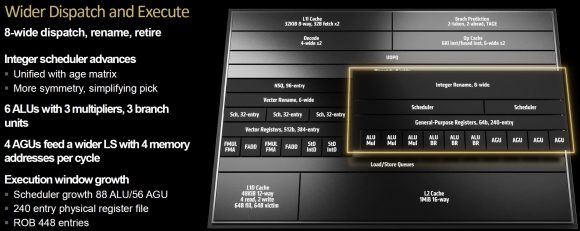

Mai departe avem motorul de executie, unde latimea de banda pentru unitatea de distribuire (Dispatch / Rename / Retire) a crescut de la 6 la 8 macro-ops / ciclu. Motorul Integer are acum 6 ALU-uri cu 3 unitati de multiplicare, un scheduler ALU imbunatatit si o fereastra de executie mai mare.

Cea mai mare schimbare este la unitatea de virgula mobila (FPU), care are acum posibilitatea de a folosi un singur vector de 512 biti pentru AVX-512, comparativ cu abordarea dual-pumped pe 256 biti din Zen 4. Acest lucru imbunatateste semnificativ performanta AVX-512 fara a reduce frecventa de lucru, ceea ce va imbunatati in consecinta si accelerarea AI.

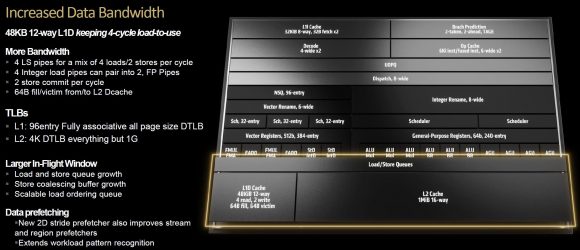

Unitatea de Incarcare / Stocare include mai multe imbunatatiri de latime de banda, care permit cresterea performantei, iar cache-urile principale (L2 si L3) sunt pastrate la aceeasi dimensiune. AMD au marit in cazul Zen 5 dimensiunea cache-ului de date L1 si asociativitatea la 48 KB 12-way (de la 32 KB 8-way in Zen 4), iar latimea de banda de la FPU la cache-ul L1D s-a dublat.

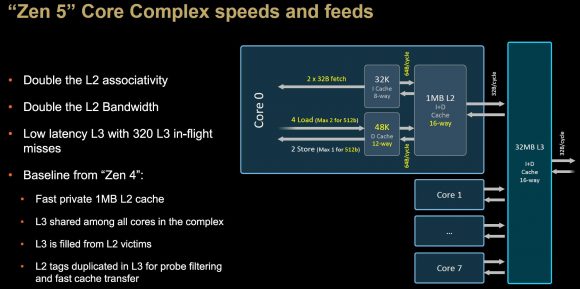

Cache-ul L2 dedicat ramane de 1 MB, insa asociativitatea impreuna cu latimea de banda sunt dublate la 64B/clk 16-way la Zen 5 (fata de 32B/clk 8-way la Zen 4).

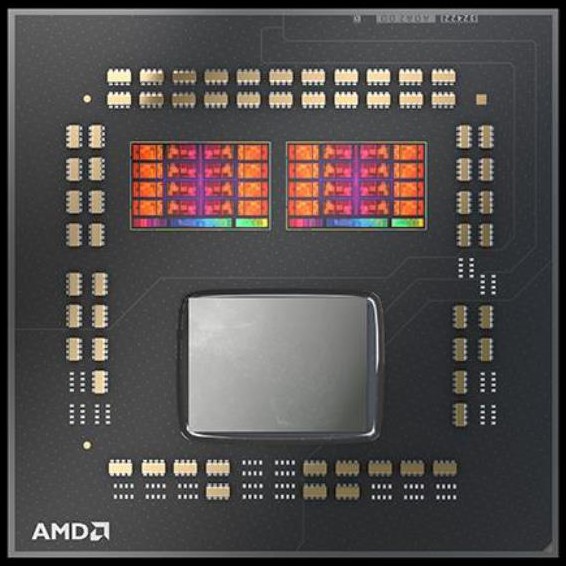

Fiecare imbunatatire arhitecturala are un impact atent evaluat asupra spatiului ocupat pe pastila de siliciu, cea mai mare portiune fiind ocupata de regula de cache-ul L2 si L3. In conditiile in care dimensiunea acestora a fost pastrata, numeroasele imbunatatiri operate de AMD ocupa spatiul extra daca este sa comparam Zen 5 cu predecesorul sau Zen 4. Vizual nu vedem mare diferenta intre CCD-urile Zen 5 comparativ cu cele Zen 4 pentru ca un rol il joaca si trecerea de la procesul TSMC N5 (5nm) la TSMC N4P (4nm).

AMD estimeaza o crestere IPC de 16% comparativ cu Zen 4, desi castigul real depinde de aplicatie. Zen 5 poate introduce mai multe instructiuni in nucleu, executandu-le simultan si imbunatatind astfel semnificativ performanta.

Comentarii