Intel Core i7: Nehalem sub microscop – partea 1

De fiecare data cand se discuta despre lansarea unui noi generatii de procesoare, inevitabil cineva aduce in discutie si legea lui Moore. Si nu e doar un cliseu, fondatorul Intel Corp. Gordon Moore a intuit foarte bine ritmul dezvoltarii circuitelor integrate inca de acum mai bine de 40 de ani, estimand ca puterea de procesare se va dubla la fiecare doi ani. Din 1965 si pana intr-o perioada relativ recenta regula s-a respectat intr-un mod intuitiv, complexitatea procesoarelor crescand in paralel cu frecventa de functionare. Dar cum totul are o limita, atingerea unei frecvente de lucru mai mari devine din ce in ce mai dificila tehnologic dar si economic asa ca o noua metoda de a spori capacitatea sistemelor de calcul isi face loc catre consumatorii obisnuiti, facand in acelasi timp ca legea lui Moore sa fie in continuare respectata. E vorba de paralelizare, ce presupune alaturarea unui numar oarecare de unitati de calcul mai simple ce cu ajutorul unui management si al unui suport competitiv sa se comporte ca o unitate mai mare si mai rapida.

Nu e nici pe departe un concept recent, CPU-urile si GPU-urile contin de ani buni multiple unitati de calcul asemanatoare ce lucreaza in paralel si isi impart munca in mod socialist pentru a creea magia electronica ce se petrece in interiorul unui calculator. Ce e nou insa e nivelul la care se face paralelizarea, orientarea de acum nemaifiind “mai multe pipelines intr-un procesor” ci “mai multe procesoare intr-un calculator”. A devenit deja transparent pentru toata lumea, din moment ce iti poti alege un sistem cu unul, doua sau patru procesoare, ba chiar opt daca ai banii de cheltuit pentru o platforma workstation, la care mai poti adauga pana la 4 placi video. Si aici vorbim doar de segmentul de piata destinat consumatorilor obisnuiti, pentru ca in zona produselor industriale oferta e si mai bogata.

Paralelismul a prins un avant serios in ultimii doi ani, fiind punctul fix de care care principalii producatori de procesoare si acceleratoare grafice aveau nevoie pentru a isi catapulta produsele de top in batalia pentru performanta. Si mai departe vom vedea cum Intel pregateste de lansare o noua generatie de procesoare care dupa specificatiile promise va fi un pas important catre, bineinteles, o paralelizare si mai buna.

Pe numele de cod “Nehalem”, noua arhitectura inglobeaza variante imbunatatite ale unitatilor de executie din arhitectura Conroe, asezonate cu multiple aditii pe care le voi expune mai tarziu dar din care amintesc cache-ul pe 3 nivele sau controller-ul de memorie integrat. Daca Penryn avea doua pastile a cate doua nuclee pe acelasi suport organic pentru a oferi un total de 4 procesoare per socket, echivalentul din generatia Nehalem va veni cu 4 nuclee integrate in aceeasi pastila si dupa cum unii prefera sa il numeasca, va fi quad-core nativ.

As vrea mai intai sa vedem din punct de vedere fizic cum e posibila o arhitectura atat de complexa. Modelul “tick-tock” pe care eminentele din Santa Clara si l-au propus a debutat in cel mai serios mod anul trecut, odata cu lansarea procesului de fabricatie pe 45nm. Din punct de vedere al performantelor momentul nu a fost crucial, insa o introspectiva in schimbarile tehnologice aduse de generatia Penryn ne ajuta sa punem mai bine in perspectiva evolutiile viitoare.

Tick-ul

Astfel, micsorarea dimensiunii tranzistoarelor de la 65nm la 45nm a fost posibila doar datorita unei cuceriri a stiintei mult mai importante, adusa la cunostinta lumii intregi sub numele de “high-k metal gate”. De aproximativ 30 de ani toate aparatele electronice folosesc tranzistoare MOS-FET (sau mai corect, IG-FET) construite cu aceleasi materiale, mai precis strat izolator din oxid de siliciu si poarta din polisilicati. Tehnologia a ajuns insa la o limita si miniaturizarea chiar si la 65nm a fost o reala problema, primele revizii confruntandu-se cu probleme termice grave cauzate de curentii de scurgere. E si normal, tranzistorii sunt atat de mici incat incap 400 de milioane intr-un centimetru patrat de chip, iar stratul izolator de oxid de siliciu a ajuns la o grosime de maxim 100 de diametre atomice. Va dati seama cum electronii voiosi mai sar gardul in partea cealalta, facand ca la inceput mai bine de jumatate din puterea consumata de un procesor pe 65nm sa fie doar “leakage current”, iar spre rafinarea tehnologiei valorile sa coboare sub 30%.

In contextul asta, o noua tehnologie de fabricare se impunea si aici faptul ca esti un gigant economic care isi permite sa cheltuie miliarde de dolari pe research & development se pare ca ajuta. Dupa ani de cercetare si testare de sute de materiale si combinatii, baietii de la Intel au stabilit ca dioxidul de siliciu si polisilicatii trebuie sa se retraga la pensie si in locul lor sa treaca la treaba portile metalice si izolatorii bazati pe hafniu. Mi-ar placea sa va spun exact despre ce metal e vorba si cineva sa imi confirme ca izolatorii sunt mai exact silicati nitriti de hafniu (HfSiON – pentru fanii lui Mendeleev), macar pentru a avea subiect de discutie la coada la Carrefour, insa companiile astea mari se pare ca au un obicei prost in a nu imparti secretele industriale cu restul lumii. Cert e insa ca in loc de 100 de diametre atomice acum se pot folosi intre 3 si 10, iar la aceeasi grosime a izolatorului curentii de scurgere sunt de 100 de ori mai mici. Destul de impresionant, dupa parerea mea.

Tock-ul

Deschizandu-si astfel o cale noua, urmatorul pas e evident evolutia arhitecturala a procesoarelor astfel incat sa beneficieze din plin de avantajele create. Si cum paralelismul e trendy in 2008, nu vom vedea un procesor mult mai rapid, ci mai degraba mai versatil si mai eficient. Nu putem nega prezenta unor optiuni ce au fost introduse de AMD da-a lungul timpului, cum ar fi controllerul de memorie integrat sau sistemul de power management ce trateaza fiecare nucleu separat. Si parca Ronak Singhal, liderul echipei ce a creat Nehalem a vazut produsul concurentei si s-a ambitionat sa arate ca poate face mai bine.

Rezultatul e unul impresionant din foarte multe puncte de vedere si asta e mare lucru mai ales pentru cei care au avut scara de valori data peste cap odata cu lansarea arhitecturii Conroe. Daca pana acum existau niste piedici tehnologice, acum faptul ca se pot inghesui pe o pastila de siliciu inspre un miliard de tranzistori odata cu trecerea la procesul de fabricatie pe 45nm permite in sfarsit ca puternica masina de calcul care este nucleul de executie Conroe sa fie pusa la munca exact asa cum trebuie, fara limitari de bandwidth cauzate de bus-ul invechit tehnologic de ceva vreme. Si ca sa nu ne mai invartim in jurul cozii, sa vedem mai exact care sunt punctele importante ale noii arhitecturi:

– quad-core si octo-core nativ

– controller de memorie DDR3 integrat

– o noua conexiune point-to-point, denumita “Quick Path Interconnect” (QPI pe scurt)

– sistem de power management inteligent, independent pe fiecare nucleu, “power gating”

– turbo mode

– L3 cache shared

– accelerator grafic on-package

– hyperthreading

– o imbunatatire cu 33% a numarului de micro-ops facute in-flight fata de nucleele Conroe

– branch prediction si TLB-uri pe cate doua nivele.

Specificatiile pentru modelele asteptate in urmatoarea perioada le regasiti in tabelul de mai jos.

Ei bine, oferta pare mai bogata ca niciodata si specificatiile sunt din cele mai interesante. Procesorul poate avea de la doua pana la 8 nuclee, de la 1 pana la 6 canale ce pot suporta 3 tipuri diferite de memorie, poate avea dimensiuni ale cache-ului L3 diferite, poate avea 1, 2 sau 4 conexiuni QPI, poate suporta variate functii de power management si poate avea pana si o alta pastiluta vecina cu el in acelasi socket pe post de accelerator grafic. Si asta nu e tot pentru ca si chipset-ul, care a devenit acum un simplu hub IO, poate avea una sau doua conexiuni QPI si 24 sau 36 de lane-uri PCI-e. Toate bucatelele astea au atat de multe moduri de a se putea combina incat cu siguranta se poate face orice pentru oricine, de la laptop-uri ultraportabile pana la agregate complexe cu destinatie industriala.

Si pentru ca e vorba de o schimbare topologica a platformei la mijlocul dintre evolutie si revolutie, asta inseamna ca avem un chipset nou: Tylersburg. Denumit comercial X58, acum a mai cedat procesorului din functii si este un simplu hub I/O cu rol de nod pentru comunicatiile dintre diverse componente ale sistemului. De fapt singularul e gresit, Tylersburg vine in patru variante cu diverse optiuni de interconectare:

– Tylersburg-24S : 1 conexiune QPI, 24 conexiuni PCI-e 2.0

– Tylersburg-24D : 2 conexiuni QPI, 24 conexiuni PCI-e 2.0

– Tylersburg-36S : 1 conexiune QPI, 36 conexiuni PCI-e 2.0

– Tylersburg-36D : 2 conexiuni QPI, 36 conexiuni PCI-e 2.0

Cele cu terminatia “D” au precum se observa doua conexiuni QPI fiecare, ceea ce inseamna ca fie vor suporta doua procesoare simultan fie vor folosi a doua conexiune pentru a se lega de un alt chipset Tylersburg, cu diverse posibilitati de combinare ulterioare. Din numarul de conexiuni PCI-e disponibile 4 sunt folosite pentru interconectarea cu southbridge-ul, ICH9/R sau ICH10/R in functie de implementare. Numarul de lane-uri ramase se pot distribui catre slot-uri PEG 8X sau 16X in diverse combinatii, rezultand suport de la una pana patru placi grafice simultan. Si acum ar cam fi momentul ca sa va dezvalui si cireasa de pe tort a platformei: nu mai ca avem suport Crossfire disponibil in orice combinatie, dar X58 vine “asezonat” cu posibilitate de activare a modului SLI, dupa o validare a implementarii de catre NVidia. Asta e o premiera pentru platformele desktop, pana acum modul SLI pe o placa de baza cu chipset Intel nefiind accesibil in mod oficial.

Bine-bine, dar cum e cu procesorul ?

.

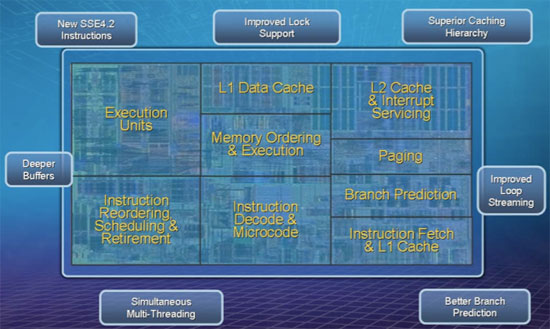

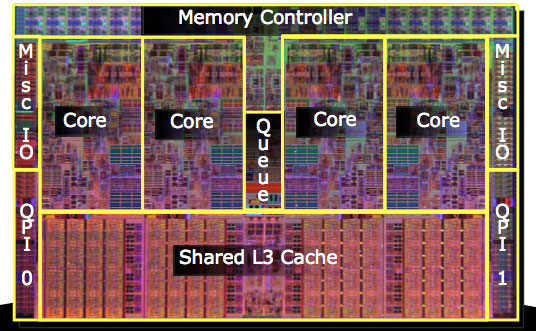

Nucleul Nehalem, celula de baza ce va alcatui noile procesoare, e infatisata in imaginea de mai sus impreuna cu punctele importante in care s-au adus modificari fata de generatia Penryn. Aceste nuclee se vor gasi in numar de doua, patru, sase sau opt integrate in aceeasi pastila, alaturi de partea numita (cu destula lipsa de imaginatie as adauga) de Intel “Uncore” pentru a forma un procesor complet. Uncore-ul va contine controller-ul de memorie, interfata QPI si cache-ul level 3. Un procesor Bloomfield cu 4 nuclee arata ca in imaginea de mai jos, unde se pot observa atent si proportiile fizice ale fiecarei componente.

Poate cea mai evidenta modificare fata de generatia anterioara e introducerea bus-ului Quick Path Interconnect (QPI), ce initial a fost denumit Common System Interface. QPI e o conexiune point-to-point packet-based cu largime mare de banda si latenta mica, ce poate atinge 6.4GT/s. “GT/s” e o unitate de masura caracteristica conexiunilor seriale de mare viteza unde semnalul de ceas e integrat in transferul de date si e prescurtarea de la “gigatransfers per second”; motivul e ca in asemenea conexiuni se foloseste o codare 8b/10b, adica 8 biti de date utilizabile sunt codate intr-un caracter cu lungimea de 10 biti. Avand in vedere ca fiecare conexiune are o largime de 20 de biti rezulta o rata de transfer de 12.8 GB/s in fiecare directie, sau 25.6 GB/s in total. Largimea maxima teoretica a bus-ului FSB in cazul lui Qx9770 de exemplu este de 12.8 GB/s si acesta trebuie sa suporte si traficul masiv de date dintre procesor si memorie.

Un prim avantaj e faptul ca acum nu va mai fi nevoie de cantitati uriase de cache pentru a compensa gatuirea frecventa a bus-ului de date, permitand folosirea tranzistorilor disponibili pentru misiuni mai importante. Nucleul de executie Conroe e o unealta foarte puternica, poate procesa simultan 4 micro-ops dar din pacate limitarile implementarii nu i-au permis folosirea la capacitate maxima; Nehalem rezolva aceasta problema, eliminand gatuirea creata de FSB si de ierarhia cache-ului.

O importanta metoda de a tine nucleele de executie cat mai ocupate e reintroducerea hyperthreading-ului. Daca in ultima aparitie HT-ul nu era o solutie prea consistenta de a obtine performanta, arhitectura Nehalem e complet diferita de cea a lui Pentium 4 si rularea simultana a cate doua thread-uri pe un procesor poate face acum diferente mari. Nehalem are o arhitectura mult mai larga si saltul urias in latimea de banda disponibila fata de generatiile anterioare il face candidatul ideal pentru reintroducerea HT.

Dar o asemenea miscare cere ajustari pe mai multe nivele. Desi unele sectiuni pot fi folosite in comun de cele doua thread-uri, altele au trebuit sa fie marite sau dublate pentru a face fata cantitatii mai mari de date. Fereastra de instructiuni a trebuit sa fie largita pentru a putea prelucra mai multe instructiuni in-flight, reorder buffer-ul stocand acum 128 de intrari fata de cele 96 in Conroe; Pentium 4 putea urmari 126 de intrari. Partitionarea e statica si in cazul rularii a doua thread-uri fiecare va avea alocat un numar de 64 de intrari disponibile. Unitatea care se ocupa de alocarea instructiunilor catre unitatile de executie (reservation station) a fost si ea marita de la 32 la 36 de intrari, dar acestea sunt partitionate dinamic.

Bufferele disponibile pentru date au fost si ele marite, load buffer-ele fiind acum 48 in loc de 32 la Conroe, iar bufferele de stocare au crescut de la 20 la 32. Si aici partitionarea e statica, dar ca si in cazul reorder buffer-ului atunci cand al 2-lea thread lipseste toate resursele vor fi alocate thread-ului care ruleaza.

In “front-end”, partea care se ocupa cu prepararea instructiunilor pentru a fi servite catre nucleul de executie, au avut loc cele mai mari schimbari fata de arhitectura Conroe. Pe masura ce arhitectura e mai paralelizata etajul de branch prediction devine mai important datorita cantitatii mai mari de date ce asteapta un rezultat al respectivei ramuri de instructiuni, asa ca Nehalem are acum un al 2-lea nivel de branch prediction. E mai lent decat primul (care a ramas neschimbat fata de Conroe) dar are o capacitate mult mai mare si sporurile de performanta aduse vor fi cel mai vizibile in lucrul cu bazele de date voluminoase. Deasemenea, tot in branch prediction s-a operat o modificare si buffer-ului “return stack” (RSB), ce acum se redenumeste pentru a evita coruperea de date in cazul unei predictii gresite; si pentru ca avem hyperthreading, RSB-ul e duplicat, fiecare thread are propriul buffer.

Si tot in tendinta catre imbunatatirea lucrului cu bazele de date avem si reorganizarea TLB-ului (Translation Lookaside Buffer). Acest buffer are rolul de a stoca corespondentele intre adresele virtuale de memorie si cele fizice, pentru a micsora timpul de acces al celor mai frecvent utilizate. Nehalem mareste capacitatea TLB-ului de instructiuni din Conroe la 128 de intrari pentru pagini mici (4k marime) si 7 intrari pentru pagini mari(2M/4M marime), iar al celui de date la 64 de intrari pentru pagini mici si 32 pentru pagini mari. Deasemenea, apare si un TLB de al 2-lea nivel, ce poate stoca 512 intrari de pagini mici.

In Conroe a fost intercalat un detector de bucle (Loop Stream Detector – LSD) intre etajul de aducere si cel de decodare a instructiunilor pentru a actiona in situatia in care urma un sir de instructiuni repetitive, oprind etajele de predictie si aducere si servind direct instructiunile din buffer-ul propriu; astfel se eliminau timpi de asteptare totodata cu economisirea de energie. Nehalem insa are acest etaj dupa partea de decodare, si in timp ce LSD-ul lui Conroe putea stoca 18 instructiuni cel al lui Nehalem stocheaza acum pana la 28 de micro-ops si le serveste direct in reorder buffer, oprind si etajul de decodare in acest timp. Spre deosebire de hyperthreading de exemplu, aceasta modificare va avea un impact egal in orice tip de mediu de lucru si va imbunatati consumul de energie cat si performanta.

Conroe introducea deasemenea o tehnica numita “macrofusion”, ce lipea doua instructiuni compare+jump inainte de decodare; Conroe ca si Nehalem are 4 decodoare de instructiuni, din care trei sunt simple si unul e complex. In cazul in care sirul de instructiuni contine numai instructiuni x86 simple, macrofusion permite decodarea a 5 instructiuni per ciclu, facand din doua simple una complexa si trimitand-o catre decodorul complex. Avantajul Nehalem e ca introduce 4 noi tipuri de perechi ce pot fi lipite in acest mod si, cel mai important, poate prelucra acum si instructiuni 64-bit.

Setul de instructiuni multimedia SSE e completat cu 7 noi adaugiri, ajungand la versiunea 4.2. Nu va asteptati la salturi masive de performanta insa la capitolul asta, exista cateva instructiuni ce accelereaza procesarea XML, o instructiune CRC32 ce ar trebui sa ajute aplicatiile de stocare si networking plus o instructiune popcount cu impact asupra identificarii tiparelor intr-un sir de date, utila de exemplu in aplicatii de recunoastere vocala sau prelucrare de secvente ADN.

Ierarhia cache pe 3 nivele e o alta noutate a lui Nehalem relativ la Conroe, si nu e noutate doar pentru ca a aparut un al 3-lea nivel ci pentru ca totul a fost regandit de sus pana jos. L1 cache ramane de aceeasi dimensiune (32k data + 32k instructiuni) dar latenta ii creste de la 3 la 4 cicli de tact. Motivul invocat de Intel e faptul ca devenea un factor limitator pentru frecventa pe noua arhitectura, iar penalizarea de performanta estimata e undeva in zona a 2-3%. L2 cache nu mai e comun ci devine privat si e restrans la numai 256k per procesor, dar i se scade latenta de la 15 la 10 cicli; deasemenea, nu mai e 24-way associative ci 8-way associative.

L3 cache-ul are 8MB in varianta Bloomfield, e 16-way associative si e inclusive – cu alte cuvinte, contine si datele existente in L1 si L2 al fiecarui procesor. Desi asta micsoreaza spatiul efectiv disponibil, imbunatateste mult coerenta traficului intern, o interogare cu raspuns negativ al L3 va insemna ca datele cautate nu exista sigur nici in L1 sau L2 si in consecinta acestea nu vor fi interogate. Cand 4 sau 8 procesoare impart acelasi cache L3 traficul parazit creat in acest fel ar putea crea penalizari vizibile de performanta. Datorita faptului ca L3 nu e parte a nucleului propriu-zis ci face parte din uncore, frecventa lui de lucru e diferita de cea a nucleelor si a celorlalte nivele de cache, ca dealtfel si tensiunea de alimentare.

Desincronizarea uncore fata de nuclee are o influenta asupra latentei L3, iar in cel mai bun caz valoarea acesteia se situeaza in zona 30-40 cicli de tact.

Sistemul de management al consumului insa face ca generatiile anterioare sa para niste piese de muzeu prafuite. De exemplu, microcontrollerul (Power Control Unit – PCU) ce se ocupa de aceasta indatorire are un numar de tranzistori mai mare decat primul 486. Acesta poate varia frecventa fiecarui nucleu din procesor in mod independent, poate intrerupe alimentarea fiecarui nucleu (power gating), poate scadea tensiunea de alimentare a nucleelor si poate deasemenea ridica frecventa unuia sau mai multor nuclee peste specificatii daca solicitarile sunt intense si nu se depasesc conditiile de design termic. Aceasta din urma functie se numeste “turbo mode” si e de fapt un sistem automat de overclocking instantaneu disponibil pe toate variantele de Core i7. Deasemenea, pentru reducerea consumului L1 cache si L2 cache folosesc celule cu 8 tranzistori in loc de 6 cum se regasesc in L3 cache, pentru a permite functionarea la o tensiune de alimentare mai redusa a nucleelor si implicit un consum imbunatatit de energie.

Toate aceste functii sunt posibile insa si datorita sistemului complex de tact. Platforma lui Nehalem ofera un semnal general de tact numit Bclock (momentan frecventa de baza e de 133Mhz), ce e folosit ca baza pentru toate frecventele procesoarelor, uncore-ului si memoriilor. Fiecare nucleu are propriul multiplicator (ce poate lua valori intre 12 si 256, dar deblocat complet doar pe i965XE) cu care se inmulteste frecventa Bclock pentru a rezulta ritmul la care va lucra respectivul nucleu. Uncore-ul are o plaja de multiplicatori intre 10 si 30, care e disponibila integral pe toate procesoarele, iar frecventa memoriei se determina impartind frecventa uncore la divizorii pentru memorii, deasemenea intreaga plaja fiind disponibila pe orice procesor. Frecventa QPI rezulta in urma inmultirii Bclock cu 18 sau 24.

Concluzie

Daca era un segment unde Intel a nu a fost la fel de puternic ca in restul domeniilor in ultimii ani, atunci acel segment e zona serverelor. Toate aceste imbunatatiri ale Core 2 care se regasesc in Core i7 au rolul de a adapta un nucleu foarte rapid la un mediu puternic paralelizat si de a ii corecta lipsurile pe care le-a avut in aplicatiile industriale. Nehalem e una din cele mai importante mutari din istoria Intel recenta si e momentul de redefinire a arhitecturii pe un termen de minim 5 ani de acum inainte.

Dupa toate aceste consideratii teoretice, e momentul sa vedem si cum stam in practica. Asadar, urmatorul articol va arata performanta noilor procesoare in diverse situatii si raportat la principalii concurenti: Intel Penryn si AMD Agena.

Comentarii

Pentru un pasionat de IT , dar cu un knowledge mediu spre .. mai jos , acest articol este pe cat de interesant , pe atat de greu de asimilat . Oricum , abia astept sa apara i7 si x58-ul aferent , sa vedem preturile .

Tin sa va felicit pentru site ( apropo , linkul cu comment pe crazypc.ro duce la water cooling 😛 ) , il vizitez destul de des pentru stiri deoarece vine vremea pt reinnoirea puterii de calcul si trebuie sa ma informez inainte de a cumpara ceva .

Succes in continuare 😀

Multumesc de comentariu si de urari !

Stiu ca e mai greu de asimilat dar e inevitabil sa faci o descriere cat mai cuprinzatoare fara sa intri destul de adanc in detalii tehnice. Performanta insa va vorbi pentru toata lumea, ca pana la urma toate imbunatatirile astea au o influenta in aplicatiile reale.

Bafta multa !

Excelent articol, M1. Keep em’ coming.

Bravo Micutu! Asteptam SLI-uri, nebunii 🙂

Foarte bun articolul. 10+

Superb articol. Excelente date prezentate in el.

Toata stima.

Bravo domnilor.Informatii bogate la indemana tuturor!

Tare de tot articolul, recunosc, unele chestii ma depasesc, chiar demult n-am mai citit un articol asa interesant si ce “avion” vor sa scoata Intel sau deja au scos. Multumesc, sunteti tari de tot, cu ocazia aceasta am aflat si de acest site.

Pingback: Intel Core i7: Nehalem sub microscop - partea 1 - My Garage

Pingback: Dreampoet’s Kingdom

Pingback: concurs AMD « Dreampoet’s Kingdom

Pingback: Intel Core i7: Nehalem sub microscop - partea 2 - lab501

Cele mai recente stiri

ADATA aniverseaza 25 de ani de existenta – mesaj de la producator

Scris in 5 May, 2026.

Intel anunta Core Ultra 7 270K Plus si Core Ultra 5 250K Plus

Scris in 11 March, 2026.

Un sistem romanesc, produs de ITD Custom Works, a ajuns tocmai in Canada, la Linus Tech Tips

Scris in 11 November, 2025.

GamesCom 2025 – Thermaltake

Scris in 21 August, 2025.

GamesCom 2025 – DeepCool

Scris in 21 August, 2025.

GamesCom 2025 – be quiet!

Scris in 21 August, 2025.

GamesCom 2025 – ASRock

Scris in 21 August, 2025.

Computex 2025 – GIGABYTE – Componente

Scris in 30 May, 2025.

Computex 2025 – Noctua

Scris in 30 May, 2025.

Computex 2025 – Pro Gamers Group – Endgame Gear, streamplify, HAVN, Kolink, Nitro Concepts

Scris in 30 May, 2025.

Syndication

Viziteaza-ne pe Facebook

Urmareste-ne pe Twitter

Vezi ce facem pe YouTube