AMD Ryzen 3000 – Part IV – DDR4 Scaling – ENGLISH Version

AIDA – Sub-latente

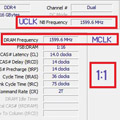

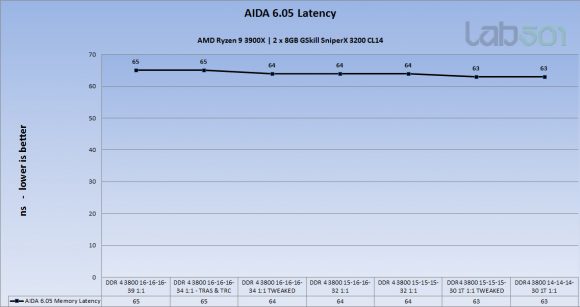

Well… I hope I have not bored you to death so far … because before get to the conclusions, we have to examine one more thing, more precisely the impact of timings and sub-timings for the same frequency. As you can see, we chose the 1: 1 DDR4 3800 configuration for this test. This configuration requires 1.4v for vDIMM and 1.07v for vSOC.

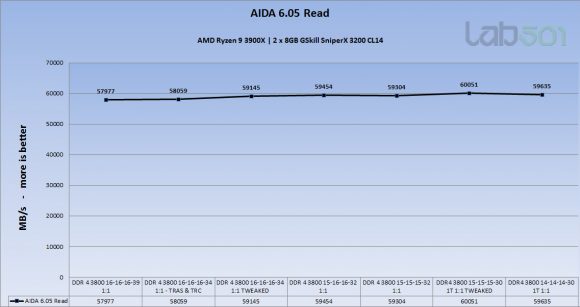

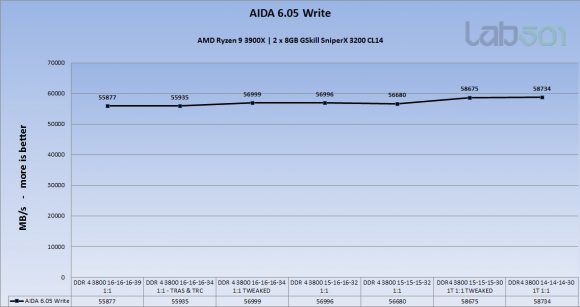

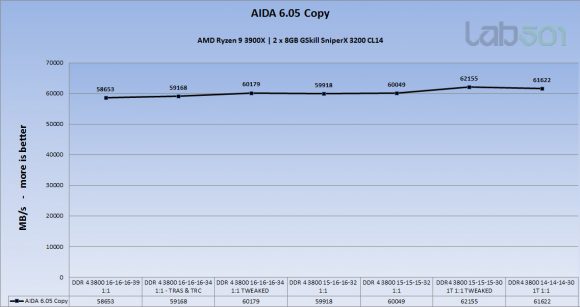

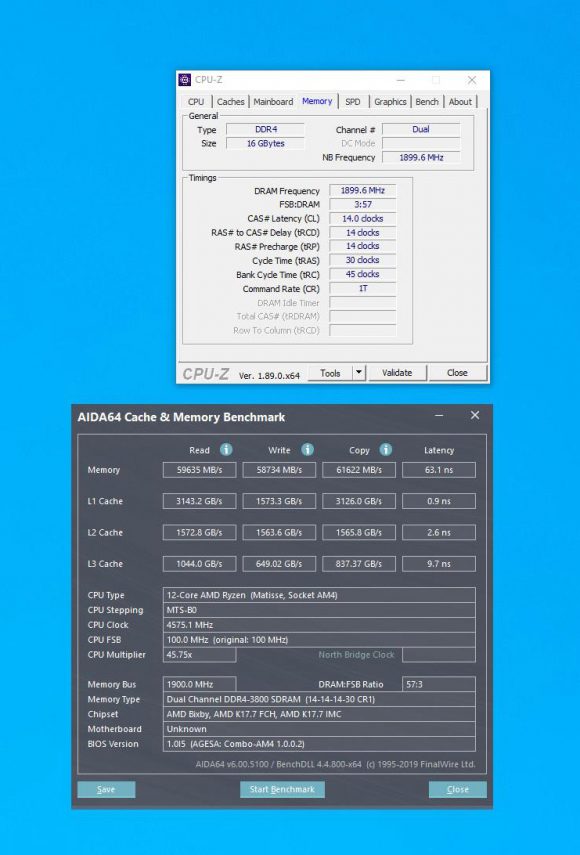

I first tested the performance with 16-16-16-39, leaving the sub-timings on AUTO. Then I tightened the tRAS and tRC and run the test again, then we optimized the performance even more by tightening the tRFC and the rest of the subtimings. Subsequently, I increased the vDIMM to 1.5v and the vSOC to 1.15v and I lowered the CAS to 15, then I set the rest of the timings and then I optimized the maximum performance for DDR4 3800 15-15-15- 30 1T 1: 1

In the last phase, I increased the vDIMM to 1.6v, and the vSOC to 1.2v and I ran the tests again for DDR4 3800 14-14-14-30 1T 1:1. From this point on, any changes in timings required a higher vDIMM, which I wasn’t really keen on feeding to the kit I use for all CPU reviews on LAB501.

However, up to this point things are pretty clear. Using a higher frequency with the 1:1 ratio is beneficial, but we can only get the maximum performance when we manually set not only the main timings, but also the sub-timings, which have a major impact on performance.

Comentarii

Niciun comentariu la: AMD Ryzen 3000 – Part IV – DDR4 Scaling – ENGLISH Version

Pingback: AMD Ryzen 3000 – Part IV – DDR4 Scaling – ENGLISH Version - 1iT.ro - Stiri IT, noutati si tehnologie

Pingback: AMD Ryzen 3000 – Part IV – DDR4 Scaling – ENGLISH Version | Stiri IT & C

Pingback: Arbeitsspeicher: Ryzen 3000 rechnet mit DDR4-3733-CL16 am schnellsten - Deutschland Nachrichten

Pingback: RAM: Ryzen 3000 expects DDR4-3733-CL16 faster – Arcynewsy

Pingback: AMD Ryzen 3000 DDR4 Scaling - Part II – Samsung B-Die vs Micron E-Die vs Hynix CJR - English version - lab501

Pingback: AMD Ryzen 3000 DDR4 Scaling - Part III – AMD Ryzen 5 3600X + B450 - English version - lab501