AMD Ryzen 3000 – Part IV – DDR4 Scaling – ENGLISH Version

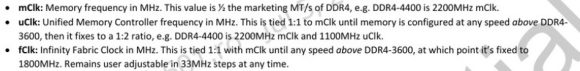

fClk, uClk, mClk

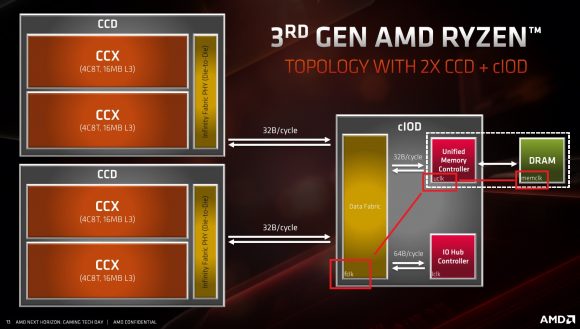

Of course, the less informed reader might wonder… what is the big news? What did AMD change? You see, if in the case of the first Zen generation the integrated memory controller (IMC) was positioned on the same die as the cores, this time the IMC is positioned in the processor’s I / O chip, which has a die of its own and is manufactured using a 12nm process, unlike the core chiplets which are manufactured using a 7nm process. Also, we have three distinct elements in the memory system, namely the Infinity Fabric (fClk), the memory controller (uClk) and the RAM (mClk). In the case of the first generations (Zen and Zen +), these were synchronized and could only work in a 1: 1: 1 ratio.

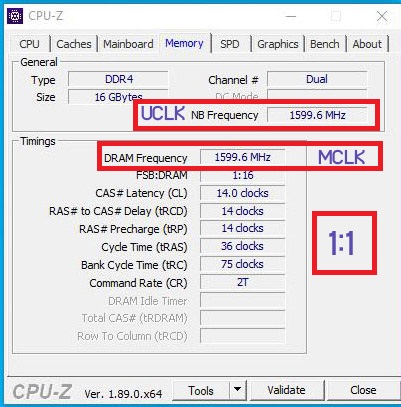

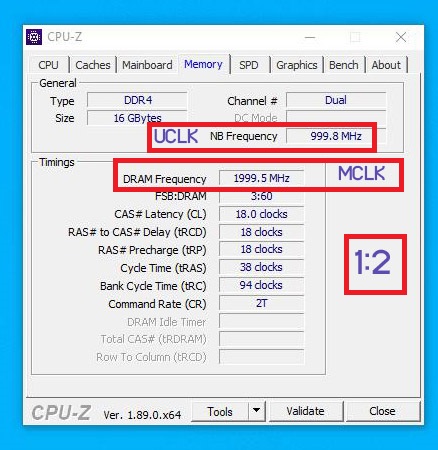

With the Zen 2 architecture, the memory can work asynchronously with the memory controller. Thus, up to DDR4 3600, including DDR4 3600, those 3 clocks are synchronized and work in 1:1 mode. Starting with DDR4 3733, the motherboard automatically chooses the 1:2 mode, where the frequency of the memory controller (uClk) and the Infinity Fabric frequency (fClk) are automatically set to half of the memory frequency (mClk). This allows us to achieve high frequencies for RAM, because the true limit in this regard is the frequency of the Infinty Fabric.

For example, most of the lower cost CPUs (Ryzen 5 3600) cannot easily pass 1800-1833 MHz fClk, the 3900X models tested so far can reach 1900MHz fClk, while rumor has it that the 3950Xs can hit 2000 MHz for fClk without too much trouble.

From the settings point of view, the ratio between uClk and mClk can be manually adjusted in BIOS – users can choose 1:1 or 1:2. The fClk frequency, on the other hand, can be adjusted individually in 33 MHz steps. However, we need to keep in mind that in order to achieve synchronous operation for settings higher than DDR4 3600, fClk must be manually set to the same value as mClk, and uClk must be set to 1:1. In this way, we get the lowest possible latency, because the memory sub-assembly works synchronously. When we have different values for fClk, uClk and mClk, the data will need to be resynchronized, which induces an increase in latency.

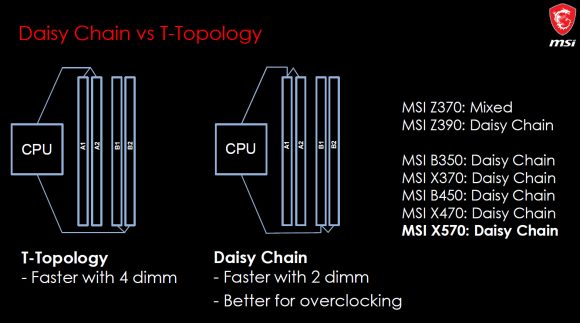

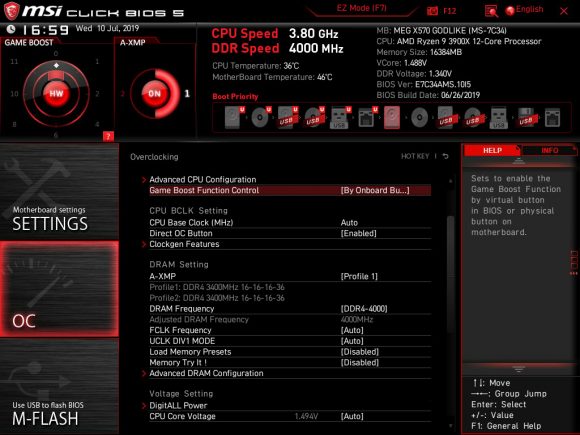

Below you can see how MSI MEG X570 Godlike bios looks like and what options do we have in regarding to RAM settings. And if I mentioned the motherboard, I must also mention the fact that the high clocks that can be reached on an X570 platform are primarily due to the possibility to set asynchronous memory to IMC and Infinity Fabric, but also because the motherboard manufacturers have given this topic a lot of attention, using server grade 8 layers PCB, short paths to memory DIMMs, and a Daisy-Chain topology for most high-end motherboards.

Comentarii

Niciun comentariu la: AMD Ryzen 3000 – Part IV – DDR4 Scaling – ENGLISH Version

Pingback: AMD Ryzen 3000 – Part IV – DDR4 Scaling – ENGLISH Version - 1iT.ro - Stiri IT, noutati si tehnologie

Pingback: AMD Ryzen 3000 – Part IV – DDR4 Scaling – ENGLISH Version | Stiri IT & C

Pingback: Arbeitsspeicher: Ryzen 3000 rechnet mit DDR4-3733-CL16 am schnellsten - Deutschland Nachrichten

Pingback: RAM: Ryzen 3000 expects DDR4-3733-CL16 faster – Arcynewsy

Pingback: AMD Ryzen 3000 DDR4 Scaling - Part II – Samsung B-Die vs Micron E-Die vs Hynix CJR - English version - lab501

Pingback: AMD Ryzen 3000 DDR4 Scaling - Part III – AMD Ryzen 5 3600X + B450 - English version - lab501